Defacto SoC Compiler whose 9.0 release was announced recently automates the SoC design creation from the first project specifications. It covers register handling, IP and connectivity insertion at RTL, UPF and SDC file generation right to logic synthesis. As part of the generation process of RTL and design collaterals, basic advanced editing and refactoring are made automated which is a major step forward for RTL design engineers and SoC architects. Indeed, design structural changes which are automated by SoC Compiler have a multi-domain awareness: physical, power, clocking and DFT.

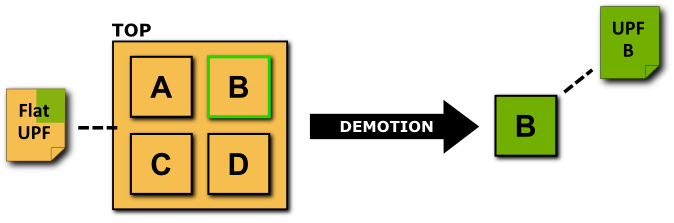

Towards domain awareness during the front-end SoC design process, a user has access to exploration, coherency checks, linting and view generation capabilities.

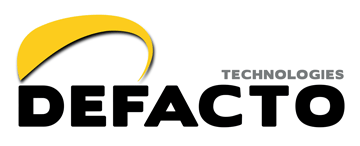

As a typical example, power awareness includes UPF linting, UPF & RTL design exploration and coherency checks, UPF file generation and UPF promotion or demotion capabilities for a top-level generation or a hierarchical UPF file extraction, respectively.

SoC Compiler can be used at different steps from user specification to logic synthesis.

Step1: Extraction, generation & update of power intent files

To manage power intent requirements a user can start by generating UPF files either from scratch or by extracting necessary files from previous projects databases. UPF updates are also automated by SoC Compiler whenever a change happens in an RTL or a gate-level description.

Step 2: Exploration, linting & coherency checks

Any generated UPF is automatically checked through design exploration capabilities and coherency checks between RTL, liberty and UPF files.

Step 3: Integration/Promotion

During SoC design assembly, UPF files are automatically promoted in conjunction with RTL files and all related files are generated, ready for synthesis.

The above automated steps for power intent management are also taken into consideration by SoC Compiler for other domains as well. The provided APIs, Python, TCL or C++ make the solution particularly easy to use, open and ready to be plugged in within internal design flows.

SoC Compiler is adopted by major SoC chip companies and recommended by top IP core providers for IP integration.

Defacto experts are hosting a LIVE webinar on June 3rd 10-11am PDT (REGISTER HERE) in which typical cases such as System Integration, RTL Integration and Power Integration will be presented.