- Details

- Parent Category: Products & Solutions

[Please note that this page is presenting an old version of our solutions. For an up to date version of our SoC Compiler please go to Products and Solutions]

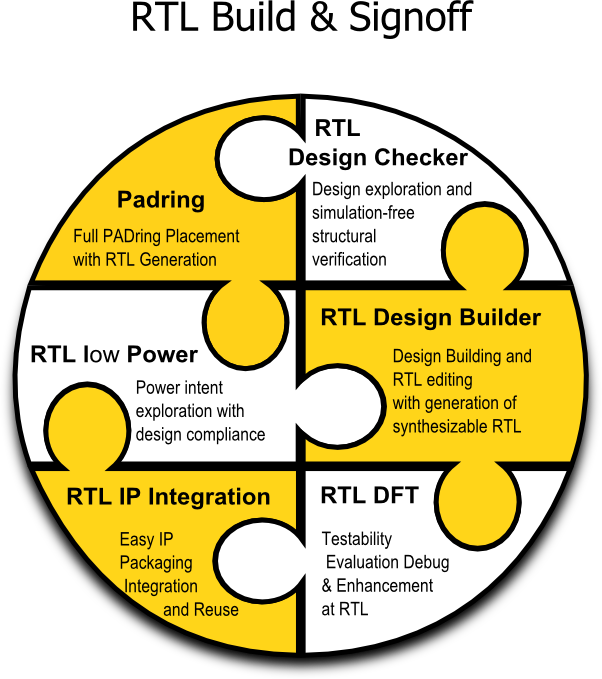

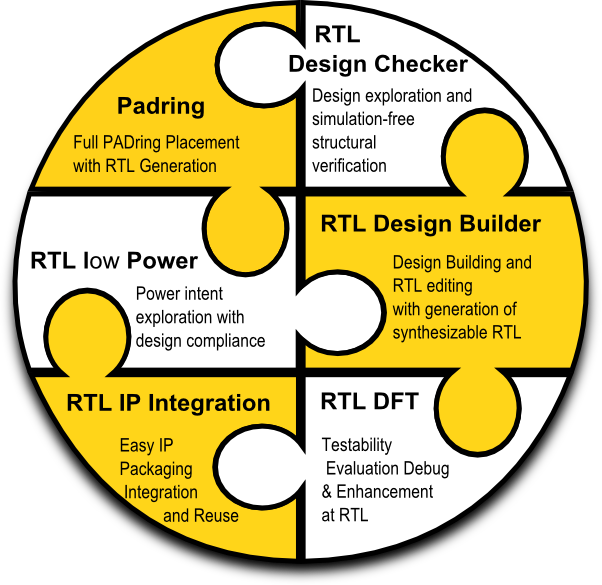

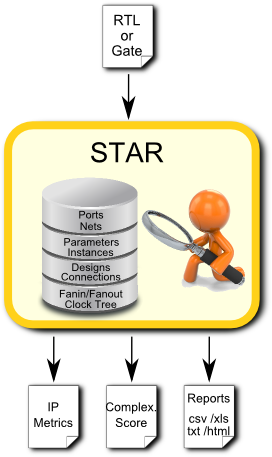

STAR is a RTL design solution which helps in design exploration, editing and structure verification. Based on set of EDA tools that work seamlessly together, build a complete solution to shorten the path towards a ready for synthesis RTL code. Through its unique “Build&Signoff” design capabilities, STAR offers to designers, in one script, the ability to extract design information, edit and generate the synthesizable RTL code and finally signoff the resulting RTL code.

Typical RTL Design Solution features are:

-

Offer flexibility, in-depth design exploration and debug through Tcl interface: query design objects, extract fanin / fanout cone, extract hierarchical paths, etc.

-

Complete set of commands for incremental editing during the same run: add / remove instance, nets, ports, create / modify connections, change instance references, rename designs etc.

-

GUI debug environment cross link: probing RTL / Schematic and coherency RTL / Gate level netlist

STAR EDA Tools :

- RTL Design Builder

- RTL Design Checker

- RTL Design For Test

- RTL low Power

- Padring

- RTL IP Integration

- RTL Code Complexity Metrics

Build custom and Language Independant Design Application at RTL with :

For More Information :

- Details

- Parent Category: Products & Solutions

[Please note that this page is presenting an old version of our solutions. For an up to date version of our SoC Compiler please go to Front-end SoC Integration]

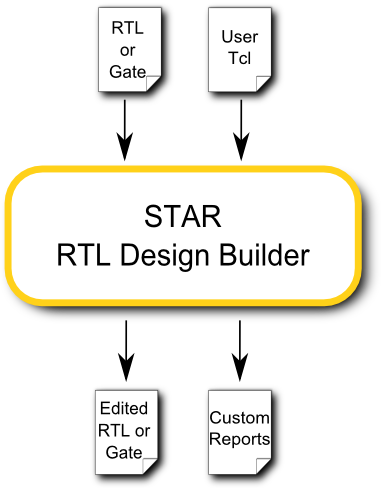

RTL Design Builder covers editing and code generation needs at RTL. It replaces complex and hard to maintain in-house scripts and tools. Through basic and advanced editing capabilities, this tool shortens the path to synthesis-ready RTL code for complex IPs and SoCs.

Typical RTL Design Builder features are :

- Basic and advanced commands with generation of ready for synthesis RTL code

- Easy development of Tcl applications for any specific editing need at RTL

- Debug environment with cross-probing between RTL and schematic

- Seamlessly integrated with the other STAR EDA tools

Additional STAR EDA Tools :

- RTL Design Checker

- RTL Design For Test

- RTL low Power

- Padring

- RTL IP Integration

- RTL Code Complexity Metrics

Build custom and Language Independant Design Application at RTL with :

For More Information :

- Details

- Parent Category: Products & Solutions

[Please note that this page is presenting an old version of our solutions. For an up to date version of our SoC Compiler please go to Checks and Verifications]

STAR CCM helps RTL Designers and Design Managers to better contain the increasing complexity of the RTL code (Verilog, VHDL, System Verilog).

Code Complexity Metrics (CCM) measure the level of complexity of an RTL code and help preventing synthesis and post-synthesis problems by pinpointing on critical areas of the code through the design hierarchy. For an RTL designer, Defacto STAR - CCM measures help flagging poorly written RTL code. For a Design Manager, such measures help estimating design effort given a new written RTL code.

Typical STAR CCM features are :

- Code complexity Score (McCabe Score)

- Hardware Metrics

- Ports

- Nets

- Parameters

- Registers

- Instances

- Designs

- Software Metrics

- File paths

- Number of (empty lines, design lines, comments lines)

- Max conditional depth

Additional STAR EDA Tools :

Build custom and Language Independant Design Application at RTL with :

For More Information :

- Details

- Parent Category: Products & Solutions

[Please note that this page is presenting an old version of our solutions. For an up to date version of our SoC Compiler please go to Products and Solutions]

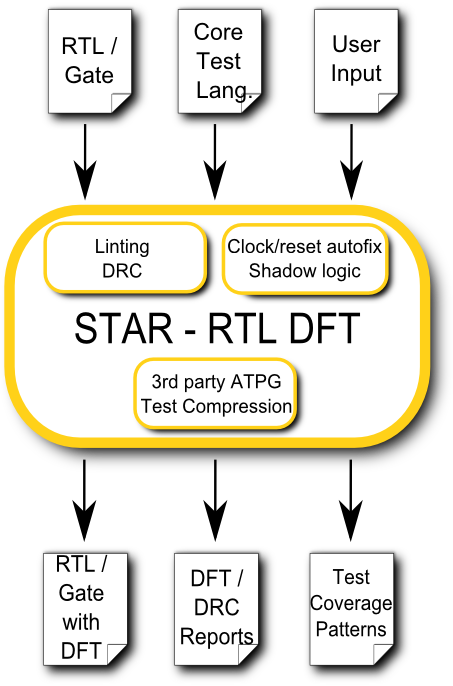

RTL DFT enables DFT engineers and designers to check the DFT quality of a design at block, IP and chip levels before releasing the RTL to synthesis. With this EDA tool, the ATPG process starts earlier and delivers accurate test coverage results sooner. Beyond running both the DRC and the ATPG processes at RTL, this tool is also used for testability enhancement and DFT planning in compliance with mainstream DFT methodologies.

Typical RTL DFT features are :

- Comprehensive Design rule checks and customizable DFT DRCs

- Enabling mainstream ATPGs to be used ahead of time, without the need of synthesis

- Pinpointing the root cause of testability weaknesses

- GUI-based DFT debug and extraction of cartography with testable and untestable IP/blocks

- Seamlessly integrated with the other STAR EDA tools

Additional STAR EDA Tools :

Build custom and Language Independant Design Application at RTL with :

For More Information :

- Details

- Parent Category: Products & Solutions

[Please note that this page is presenting an old version of our solutions. For an up to date version of our SoC Compiler please go to Checks and Verifications]

RTL Design Checker enables complete access to the design database through queries that allow in-depth design exploration and GUI debugging tasks. The tool automatically and cost-effectively performs general purpose connectivity checks for a large number of pins simulation-free. Through the design hierarchy, this tool helps verify and debug multiple connections under different modes of operation within the same run.

Typical RTL Checker features are :

- In-depth design exploration through Tcl interface

- Simulation-free Pin-to-Pin tracing

- Easy creation of Tcl custom checks

- GUI exploration

- Cyclomatic Code Complexity extraction

- Seamlessly integrated with the other STAR EDA tools

Additional STAR EDA Tools :

- RTL Design Builder

- RTL Design For Test

- RTL low Power

- Padring

- RTL IP Integration

- RTL Code Complexity Metrics

Build custom and Language Independant Design Application at RTL with :