The Automated SoC Design from Specification and Exploration to RTL Generation by Achieving Cost-effectiveness and Sustainability

With the miniaturization of components, transistor density is increasing faster than the productivity of system-on-chip designers and the improvement of EDA tools. Therefore, the SoC Planner Project aims to provide system-on-chip designers with a solution to the explosion in design costs, particularly for advanced nodes.

This project intends to develop an innovative and indispensable reference software suite for all hardware designers, enabling automatic configuration and planning of the next generation of system-on-chips, guaranteeing the best compromise regarding cost, performance, and eco-design criteria.

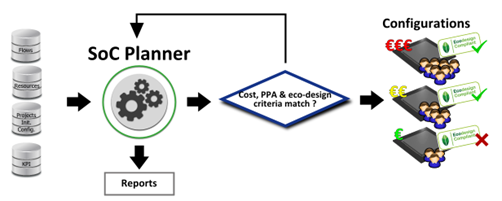

The main novelty of the SoC Planner project is to limit the number of possible configurations for a complex system-on-chip from the very start of a new design project. It is usual to have hundreds of thousands or even millions of possible configurations for a single project.

SoC Planner innovation will drastically reduce this number to a set of relevant configurations in line with the scope of the designer specifications at early stages. This will significantly reduce the number of design cycles (iterations of the product development) and, consequently, development cost savings. An eco-design dimension is also taken into account to enable precise measurement of environmental impact at the start of a new system-on-chip design project, and the minimization of this criterion in the same way as the usual performance criteria (consumption, time, surface area).

SoC Planner addresses sustainability at the early stages of SoC design by integrating eco-friendly principles throughout every step of the design process. SoC Planner combines the strength of several tools from CEA, Defacto Technologies and Innova Advanced Technologies. Through a user-friendly graphical interface, SoC Planner automates the exploration and optimization of computing architecture designs to find the most suitable configurations and generate the related SoC RTL design automatically.

This project was funded by BPI France as part of the France 2030 program.